# 5DV008 Computer Architecture Umeå University Department of Computing Science

Stephen J. Hegner

# Topic 2: Instructions Part C: Control Flow

These slides are mostly taken verbatim, or with minor changes, from those prepared by

Mary Jane Irwin (www.cse.psu.edu/~mji)

of The Pennsylvania State University

[Adapted from Computer Organization and Design, 4<sup>th</sup> Edition,

Patterson & Hennessy, © 2008, MK]

11/23/09 5DV008 20091111 t:2C sl:1 1

## **Key to the Slides**

- The source of each slide is coded in the footer on the right side:

- Irwin CSE331 = slide by Mary Jane Irwin from the course CSE331 (Computer Organization and Design) at Pennsylvania State University.

- Irwin CSE431 = slide by Mary Jane Irwin from the course CSE431 (Computer Architecture) at Pennsylvania State University.

- Hegner UU = slide by Stephen J. Hegner at Umeå University.

11/23/09 5DV008 20091111 t:2C sl:2

2

Hegner Ul

Heaner UU

# Review: R Format Instructions

- R format op rs rt rd shamt funct

6 bits 5 bits 5 bits 5 bits 5 bits 6 bits

- Arithmetic instructions

add \$t0, \$s1, \$s2

sub \$t0, \$s1, \$s2

0x00

17

18

8

0

0x20

add

0x00

17

18

8

0

0x22

sub

sll \$t0, \$s1, 4 srl \$t0, \$s1, 4 sra \$t0, \$s1, 4

| Į | 0x00 | 17 | 8 | 4 | 0x00 | sll |

|---|------|----|---|---|------|-----|

| [ | 0x00 | 17 | 8 | 4 | 0x02 | srl |

|   | 0x00 | 17 | 8 | 4 | 0x03 | sra |

and \$t0, \$s1, \$s2 or \$t0, \$s1, \$s2 nor \$t0, \$s1, \$s2

| 0x00 | 17 | 18 | 8 | 0 | 0x24 | and |

|------|----|----|---|---|------|-----|

| 0x00 | 17 | 18 | 8 | 0 | 0x25 | or  |

| 0×00 | 17 | 18 | ρ | 0 | 0x27 | noi |

5DV008 20091111 t:2C sl:3

#### **MIPS Control Flow Instructions**

□ MIPS conditional branch instructions:

bne \$s0, \$s1, Lb1 #go to Lb1 if  $s0\neq s1$  beq \$s0, \$s1, Lb1 #go to Lb1 if s0=s1

• Ex: if (i==j) h = i + j; bne \$s0, \$s1, Lb11 add \$s3, \$s0, \$s1 Lb11: ...

□ Instruction Format (I format):

|  | go   | rs | rt | 16-bit value |

|--|------|----|----|--------------|

|  |      |    |    |              |

|  | 0x05 | 16 | 17 | ???          |

How is the branch destination address specified?

5DV008 20091111 t:2C sl:5

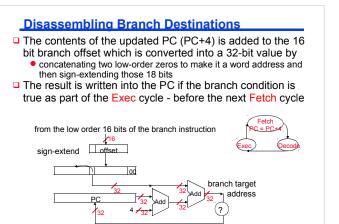

# Specifying Branch Destinations

- $\hfill\Box$  Could specify the memory address of the branch target

- but that would require a 32-bit field

bne \$s0,\$s1,Lbl1

dd \$s3,\$s0,\$s1

- Could use a "base" register and add to it the 16-bit offset

- which register?

- Instruction Address Register

(PC = program counter) its use is

automatically implied by branch

- PC gets updated (PC+4) during the Fetch cycle so that it holds the address of the next instruction

- limits the branch distance to

- -2<sup>5</sup> to +2<sup>5</sup>-1 instr's from the (instruction after the) branch

- but most branches are local anyway

5DV008 20091111 t:2C sl:6

Lbl1:

Irwin CSE331 PSU

| <br> |  |  |

|------|--|--|

|      |  |  |

|      |  |  |

|      |  |  |

|      |  |  |

#### Offset Tradeoffs

5DV008 20091111 t:2C sl:7

- Why not just store the word offset in the low order 16 bits? Then the two low order zeros wouldn't have to be concatenated, it would be less confusing, ...

- □ That would limit the branch distance to -2<sup>th</sup> to +2<sup>th</sup> -1 instructions from the (instruction after the) branch

- And concatenating the two zero bits costs us very little in additional hardware and has no impact on the clock cycle time

5DV008 20091111 t:2C sl:8

Irwin CSE331 PSU

Irwin CSE331 PSU

#### **Assembling Branches Example**

Assembly code

bne \$s0, \$s1, Lb11 add \$s3, \$s0, \$s1

Lbl1: ..

■ Machine Format of bne:

|      |    |    | 16-bit offset | I format   |

|------|----|----|---------------|------------|

| οp   | IS |    | 16-DIL OHSEL  | 1 10111141 |

|      |    | Ä  | J.            |            |

| 0x05 | 16 | 17 |               |            |

- Remember

- After the bne instruction is fetched, the PC is updated so that it is addressing the add instruction

- The offset (plus 2 low-order zeros) is sign-extended and added to the (updated) PC

5DV008 20091111 t:2C sl:9

| • |  |  |  |

|---|--|--|--|

|   |  |  |  |

|   |  |  |  |

|   |  |  |  |

|   |  |  |  |

|   |  |  |  |

|   |  |  |  |

|   |  |  |  |

|   |  |  |  |

|   |  |  |  |

|   |  |  |  |

|   |  |  |  |

|   |  |  |  |

|   |  |  |  |

|   |  |  |  |

|   |  |  |  |

|   |  |  |  |

|   |  |  |  |

|   |  |  |  |

|   |  |  |  |

|   |  |  |  |

|   |  |  |  |

|   |  |  |  |

|   |  |  |  |

|   |  |  |  |

|   |  |  |  |

|   |  |  |  |

|   |  |  |  |

|   |  |  |  |

|   |  |  |  |

|   |  |  |  |

|   |  |  |  |

|   |  |  |  |

|   |  |  |  |

|   |  |  |  |

|   |  |  |  |

|   |  |  |  |

|   |  |  |  |

|   |  |  |  |

|   |  |  |  |

|   |  |  |  |

|   |  |  |  |

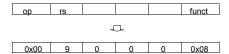

### **Assembling Branches Example** Assembly code bne \$s0, \$s1, Lb11 add \$s3, \$s0, \$s1 Lb11: Machine Format of bne: I format op rs rt 16-bit offset ட 0x05 16 17 0x0001 Remember • After the bne instruction is fetched, the PC is updated so that it is addressing the add instruction • The offset (plus 2 low-order zeros) is sign-extended and added to the (updated) PC 5DV008 20091111 t:2C sl:10 Irwin CSE331 PSU **In Support of Branch Instructions** □ We have beq, bne, but what about other kinds of branches (e.g., branch-if-less-than)? For this, we need yet another instruction, slt Set on less than instruction: # if \$s0 < \$s1 slt \$t0, \$s0, \$s1 then # \$t0 = 1 # \$t0 = 0 else Instruction format (R format): 0x00 16 17 8 ■ Alternate versions of slt slti \$t0, \$s0, 25 # if \$s0 < 25 then \$t0=1 ... sltu \$t0, \$s0, \$s1 # if \$s0 < \$s1 then \$t0=1 ... sltiu \$t0, \$s0, 25 # if \$s0 < 25 then \$t0=1 ... 5DV008 20091111 t:2C sl:11 Irwin CSE331 PSU **More Branch Instructions** □ Can use slt, beq, bne, and the fixed value of 0 in register \$zero to create other conditions less than blt \$s1, \$s2, Label less than or equal to ble \$s1, \$s2, Label bgt \$s1, \$s2, Label greater than • great than or equal to bge \$s1, \$s2, Label Such branches are included in the instruction set as pseudo instructions - recognized (and expanded) by the assembler Its why the assembler needs a reserved register (\$at)

Irwin CSE331 PSU

5DV008 20091111 t:2C sl:12

# **More Branch Instructions**

less than

greater than

□ Can use slt, beq, bne, and the fixed value of 0 in register \$zero to create other conditions

```

slt $at, $s1, $s2  #$at set to 1 if

bne $at, $zero, Label #$s1 < $s2

• less than or equal to ble $s1, $s2, Label

```

blt \$s1, \$s2, Label

bgt \$s1, \$s2, Label

- Such branches are included in the instruction set as pseudo instructions - recognized (and expanded) by the assembler

- Its why the assembler needs a reserved register (\$at)

• great than or equal to bge \$s1, \$s2, Label

\_\_\_\_\_

Irwin CSE331 PSU

#### **Another Instruction for Changing Flow**

MIPS also has an unconditional branch instruction or jump instruction:

5DV008 20091111 t:2C sI:14

Irwin CSE331 PSU

#### Assembling Jumps

Instruction:

j Lbl

#go to Lbl

■ Machine Format (J format):

| ор   | 26-bit address |

|------|----------------|

|      | <u>.</u>       |

| 0x02 | 2222           |

- □ How is the jump destination address specified?

- As an absolute address formed by

- concatenating 00 as the 2 low-order bits to make it a word address

- concatenating the upper 4 bits of the current PC (now PC+4)

5DV008 20091111 t:2C sl:15

#### **Disassembling Jump Destinations**

- □ The low-order 26 bits of the jump instruction is converted into a 32-bit jump destination address by

- concatenating two low-order zeros to create an 28 bit (word) address and then concatenating the upper 4 bits of the current PC (now PC+4) to create a 32 bit (word) address

that is put into the PC prior to the next Fetch cycle

from the low order 26 bits of the jump instruction

5DV008 20091111 t:2C sl:16

Irwin CSE331 PSU

#### **Branching Far Away**

- What if the branch destination is further away than can be captured in 16 bits?

- □ The assembler comes to the rescue it inserts an unconditional jump to the branch target and inverts the condition

#### becomes

5DV008 20091111 t:2C sl:17

Irwin CSE331 PSU

# Assembling Branches and Jumps

□ Assemble the MIPS machine code for the following code sequence. Assume that the addr of the beg instr is 0x00400020<sub>k</sub>

|       | beq | \$s0, | \$s1, | Else |

|-------|-----|-------|-------|------|

|       | add | \$s3, | \$s0, | \$s1 |

|       | j   | Exit  |       |      |

| Else: | sub | \$s3, | \$s0, | \$s1 |

| Exit: |     |       |       |      |

5DV008 20091111 t:2C sl:18

#### **Assembling Branches and Jumps**

□ Assemble the MIPS machine code for the following code sequence. Assume that the addr of the beq instr is 0x00400020<sub>k</sub>

```

$s0, $s1, Else

$s3, $s0, $s1

Exit

beq

add

sub $s3, $s0, $s1

Exit:

0x00400020

16

17

16 17 19 0 0×20

0x00400024

0

0x00400028

2

0000 0100 0 ... 0 0011 002

jmp dst = (0x0) 0x040003 00<sub>2</sub>(00_2)

= 0 \times 00400030

0x0040002c

0

17 19 0 0x22

0x00400030

5DV008 20091111 t:2C sl:19

Irwin CSE331 PSU

```

#### **Compiling While Loops**

□ Compile the assembly code for the C while loop where i is in \$s0, j is in \$s1, and k is in \$s2

```

while (i!=k)

i=i+j;

```

Basic block – A sequence of instructions without branches (except at the end) and without branch targets (except at the beginning)

5DV008 20091111 t:2C sl:20

Irwin CSE331 PSU

# Compiling While Loops

□ Compile the assembly code for the C while loop where i is in \$s0, j is in \$s1, and k is in \$s2

```

while (i!=k)

i=i+j;

Loop: beq $s0, $s2, Exit

add $s0, $s0, $s1

j Loop

Exit: . . .

```

□ Basic block – A sequence of instructions without branches (except at the end) and without branch targets (except at the beginning)

5DV008 20091111 t:2C sl:21

| - |  |  |

|---|--|--|

|   |  |  |

|   |  |  |

# Compiling Another While Loop

□ Compile the assembly code for the C while loop where i is in \$s0, k is in \$s1, and the base address of the array save is in \$s2

```

while (save[i] == k)

i += 1;

```

5DV008 20091111 t:2C sI:22

Irwin CSE331 PSU

# **Compiling Another While Loop**

□ Compile the assembly code for the C while loop where i is in \$s0, k is in \$s1, and the base address of the array save is in \$s2

```

while (save[i] == k)

i += 1;

Loop:    sll $t1, $s0, 2

add $t1, $t1, $s2

lw $t0, 0($t1)

bne $t0, $s1, Exit

addi $s0, $s0, 1

j Loop

Exit: . . .

```

5DV008 20091111 t:2C sl:23

Irwin CSE331 PSU

# Yet Another Instruction for Changing Flow

- Most higher level languages have case or switch statements allowing the code to select one of many alternatives depending on a single value

- Instruction:

jr \$t1

#go to address in \$t1

Machine format (R format):

5DV008 20091111 t:2C sI:24

#### Compiling a Case (Switch) Statement

```

switch (k) {

case 0: h=i+j; break; /*k=0*/

case 1: h=i+h; break; /*k=1*/

case 2: h=i-j; break; /*k=2*/

```

□ Assume three sequential words in memory starting at the address in \$t4 have the addresses of the labels L0, L1, and L2 and k is in \$s2

|       | Memory |

|-------|--------|

|       | L2     |

|       | L1     |

| \$t4→ | LO     |

|       |        |

|       |        |

```

add

$t1, $s2, $s2

#$t1 = 2 * k

#$t1 = 4 * k

#$t1 = addr of JumpT[k]

#$t0 = JumpT[k]

$t1, $t1, $t1

$t1, $t1, $t4

add

add

lw

$t0, 0($t1)

#jump based on $t0

$t.0

$s3, $s0, $s1

#k=0 so h=i+j

L0:

add

Exit

$s3, $s0, $s3

add

#k=1 so h=i+h

L1:

Exit

T.2 ·

sub

$s3, $s0, $s1

\#k=2 so h=i-j

```

Irwin CSE331 PSU

#### **Programming Styles**

- Procedures (subroutines, functions) allow the programmer to structure programs making them

- easier to understand and debug and

- allowing code to be reused

- Procedures allow the programmer to concentrate on one portion of the code at a time

- parameters act as barriers between the procedure and the rest of the program and data, allowing the procedure to be passed values (arguments) and to return values (results)

5DV008 20091111 t:2C sl:26

Irwin CSE331 PSU

#### Six Steps in Execution of a Procedure

- Main routine (caller) places parameters in a place where the procedure (callee) can access them

- \$a0 \$a3: four argument registers

- 2. Caller transfers control to the callee

- 3. Callee acquires the storage resources needed

- 4. Callee performs the desired task

- Callee places the result value in a place where the caller can access it

- \$v0 \$v1: two value registers for result values

- 6. Callee returns control to the caller

- \$ra: one return address register to return to the point of origin

5DV008 20091111 t:2C sl:27

| Review: MIPS | <u>S Register Nan</u> | <u>ning Conventio</u> | n |

|--------------|-----------------------|-----------------------|---|

|--------------|-----------------------|-----------------------|---|

| Nick<br>Name | Register<br>Number | Usage                  | Preserve on call? |

|--------------|--------------------|------------------------|-------------------|

| \$zero       | 0                  | constant 0 (hardware)  | n.a.              |

| \$at         | 1                  | reserved for assembler | n.a.              |

| \$v0 - \$v1  | 2-3                | returned values        | no                |

| \$a0 - \$a3  | 4-7                | arguments              | yes               |

| \$t0 - \$t7  | 8-15               | temporaries            | no                |

| \$s0 - \$s7  | 16-23              | saved values           | yes               |

| \$t8 - \$t9  | 24-25              | temporaries            | no                |

| \$k0 - \$k1  | 26-27              | reserved for OS        | n.a.              |

| \$gp         | 28                 | global pointer         | yes               |

| \$sp         | 29                 | stack pointer          | yes               |

| \$fp         | 30                 | frame pointer          | yes               |

| \$ra         | 31                 | return addr (hardware) | yes               |

5DV008 20091111 t:2C sl:28

Irwin CSE331 PSU

# Instruction for Calling a Procedure

□ MIPS procedure call instruction:

jal ProcAddress

#jump and link

- Saves PC+4 in register \$ra as the link to the following instruction to set up the procedure return

- Machine format (J format):

| ор   | 26 bit address |

|------|----------------|

|      | <b>'</b>       |

| 0x03 | ????           |

☐ Then can do procedure return with just

jr \$ra #return

5DV008 20091111 t:2C sI:29

Irwin CSE331 PSU

#### **Basic Procedure Flow**

□ For a procedure that computes the GCD of two values i (in \$t0) and j (in \$t1)

gcd(i,j);

$\hfill\Box$  The caller puts the  $\pm$  and  $\dag$  (the parameters values) in a0 and a1 and issues a

jal gcd #jump to routine gcd

☐ The callee computes the GCD, puts the result in \$v0, and returns control to the caller using

gcd: . . . #code to compute gcd

jr \$ra #return

5DV008 20091111 t:2C sl:30

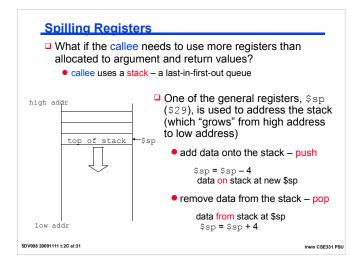

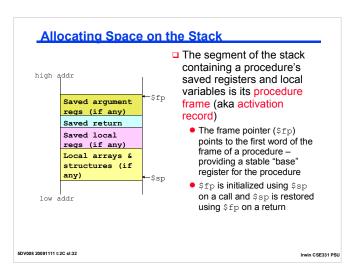

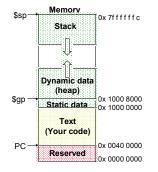

#### Allocating Space on the Heap

- ☐ There is a static data segment area for storing constants and other static variables (e.g., arrays)

- And a dynamic data segment (aka heap) area for structures that grow and shrink (e.g., linked lists)

- Allocate space on the heap with malloc() and free it with free() in C

Irwin CSE331 PSU

5DV008 20091111 t:2C sI:33

#### Compiling a C Leaf Procedure

```

□ Leaf procedures are ones that do not call other procedures. Give the MIPS assembler code for int leaf_ex (int g, int h, int i, int j) { int f; f = (g+h) - (i+j); return f; } where g, h, i, and j are in $a0, $a1, $a2, $a3

```

5DV008 20091111 t:2C sI:34

5DV008 20091111 t:2C sl:35

Irwin CSE331 PSU

# Compiling a C Leaf Procedure

```

Leaf procedures are ones that do not call other

procedures. Give the MIPS assembler code for

int leaf_ex (int g, int h, int i, int j)

{ int f;

f = (g+h) - (i+j);

return f; }

where g, h, i, and j are in $a0, $a1, $a2, $a3

$sp,$sp,-8

$t1,4($sp)

$t0,0($sp)

#make stack room

leaf ex: addi

#save $t1 on stack

SW

#save $t0 on stack

add

$t0,$a0,$a1

$t1,$a2,$a3

$v0,$t0,$t1

$t0,0($sp)

add

sub

lw

#restore $t0

$t1,4($sp)

#restore $t1

addi

$sp,$sp,8

#adjust stack ptr

jr

$ra

```

# **Nested Procedures**

What happens to return addresses with nested procedures?

```

int rt 1 (int i) {

if (i == 0) return 0;

else return rt_2(i-1); }

caller: jal rt_1

next:

. . .

bne $a0, $zero, to_2

add $v0, $zero, $zero

rt 1:

jr

$ra

to_2:

addi $a0, $a0, -1

jal rt 2

jr

$ra

rt 2:

```

5DV008 20091111 t:2C sI:36

Irwin CSE331 PSU

#### Nested Procedures Outcome

```

caller: jal rt_1

next: . . . .

rt_1: bne $a0, $zero, to_2

add $v0, $zero, $zero

jr $ra

to_2: addi $a0, $a0, -1

jal rt_2

jr $ra

rt_2: . . .

```

On the call to rt\_1, the return address (next in the caller routine) gets stored in \$ra. What happens to the value in \$ra (when i != 0) when rt\_1 makes a call to rt\_2?

5DV008 20091111 t:2C sl:37

Irwin CSE331 PSU

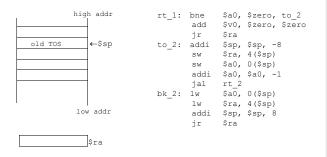

#### Saving the Return Address. Part 1

□ Nested procedures (i passed in \$a0, return value in \$v0)

```

rt_1: bne $a0, $zero, to_2

add $v0, $zero, $zero

jr

$ra

←$sp

old TOS

to 2: addi $sp, $sp, -8

$ra, 4($sp)

sw

$a0, 0($sp)

addi

$a0, $a0, -1

jal

rt_2

bk_2: lw

$a0, 0($sp)

$ra, 4($sp)

low addr

addi

$sp, $sp, 8

jr

$ra

```

Save the return address (and arguments) on the stack

5DV008 20091111 t:2C sl:38

Irwin CSE331 PSU

#### Saving the Return Address, Part 1

□ Nested procedures (i passed in \$a0, return value in \$v0)

```

$a0, $zero, to_2

$v0, $zero, $zero

high addr

pc \rightarrow rt_1: bne

add

$ra

jr

$pc → to_2: addi

$sp, $sp, -8

pc \rightarrow

SW

$ra, 4($sp)

caller rt addr

$a0, 0($sp)

pc \rightarrow

SW

addi

$a0, $a0, -1

jal

rt 2

$a0, 0($sp)

1 w

$ra, 4($sp)

addi

$sp, $sp, 8

low addr

$ra

jr

$ra

```

$\hfill \square$  Save the return address (and arguments) on the stack

5DV008 20091111 t:2C sl:39

#### Saving the Return Address. Part 2

□ Nested procedures (i passed in \$a0, return value in \$v0)

□ Save the return address (and arguments) on the stack

5DV008 20091111 t:2C sI:40

Irwin CSE331 PSU

#### Saving the Return Address. Part 2

□ Nested procedures (i passed in \$a0, return value in \$v0)

```

rt_1: bne

$a0, $zero, to_2

add

$v0, $zero, $zero

$ra

←$sp

$sp, $sp, -8

old TOS

to_2: addi

caller rt addr

sw

$ra, 4($sp)

$a0, 0($sp)

old $a0

SW

addi

$a0, $a0, -1

jal

rt_2

bk_2: lw

$a0, 0($sp)

$ra, 4($sp)

lw

pc \rightarrow

addi

$sp, $sp, 8

low addr

pc \rightarrow

caller rt addr $ra

```

□ Save the return address (and arguments) on the stack

5DV008 20091111 t:2C sl:41

Irwin CSE331 PSU

# Compiling a Recursive Procedure

□ A procedure for calculating factorial

```

int fact (int n) {

if (n < 1) return 1;

else return (n * fact (n-1)); }</pre>

```

□ A recursive procedure (one that calls itself!)

```

fact (0) = 1

fact (1) = 1 * 1 = 1

fact (2) = 2 * 1 * 1 = 2

fact (3) = 3 * 2 * 1 * 1 = 6

fact (4) = 4 * 3 * 2 * 1 * 1 = 24

```

□ Assume n is passed in \$a0; result returned in \$v0

5DV008 20091111 t:2C sI:42

#### Compiling a Recursive Procedure fact: addi \$sp, \$sp, -8 SW

#adjust stack pointer \$ra, 4(\$sp) #save return address sw \$a0, 0(\$sp) #save argument n slti \$t0, \$a0, 1 #test for n < 1 \$t0, \$zero, L1 #if  $n \ge 1$ , go to L1 beq \$v0, \$zero, 1 #else return 1 in \$v0 addi addi \$sp, \$sp, 8 #adjust stack pointer

#return to caller  $(1^{\pm})$ jr \$ra L1: addi \$a0, \$a0, -1 #n >=1, so decrement n jal fact #call fact with (n-1)

#this is where fact returns bk\_f:lw \$a0, 0(\$sp) #restore argument n 1 w \$ra, 4(\$sp) #restore return address addi \$sp, \$sp, 8 mul \$v0, \$a0, \$v0 #adjust stack pointer #\$v0 = n \* fact(n-1)jr \$ra #return to caller  $(2^{nl})$

5DV008 20091111 t:2C sl:43 Irwin CSE331 PSU

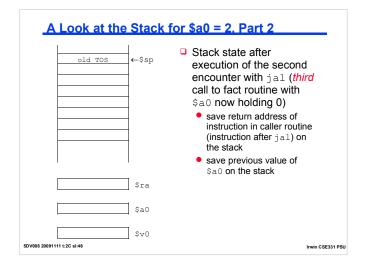

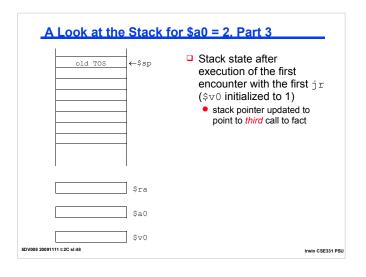

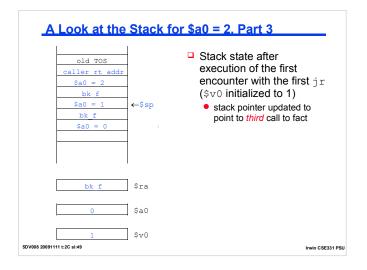

#### A Look at the Stack for \$a0 = 2. Part 1

5DV008 20091111 t:2C sl:44

- Stack state after execution of the first encounter with jal (second call to fact routine with \$a0 now holding 1)

- saved return address to caller routine (i.e., location in the main routine where first call to fact is made) on the stack

- saved original value of \$a0 on the stack

Irwin CSE331 PSU

#### A Look at the Stack for \$a0 = 2. Part 1

\$a0

- Stack state after execution of the first encounter with jal (second call to fact routine with \$a0 now holding 1)

- saved return address to caller routine (i.e., location in the main routine where first call to fact is made) on the stack

- saved original value of \$a0 on the stack

\$v0 5DV008 20091111 t:2C sl:45

\$a0

#### A Look at the Stack for \$a0 = 2. Part 2 Stack state after old TOS execution of the second caller rt addr encounter with jal (third call to fact routine with \$a0 = 1 **←**\$sp \$a0 now holding 0) saved return address of instruction in caller routine (instruction after jal) on the stack saved previous value of \$a0 on the stack \$ra \$a0 \$v0 5DV008 20091111 t:2C sl:47 Irwin CSE331 PSU

#### A Look at the Stack for \$a0 = 2. Part 4 Stack state after execution **←**\$sp old TOS of the first encounter with the second jr (return from fact routine after updating \$v0 to 1 \* 1) return address to caller routine (bk\_f in fact routine) restored to \$ra from the stack previous value of \$a0 restored from the stack stack pointer updated to \$ra point to second call to fact \$a0 5DV008 20091111 t:2C sl:50 Irwin CSE331 PSU

#### A Look at the Stack for \$a0 = 2. Part 4 Stack state after execution old TOS of the first encounter with caller rt addr the second jr (return from **←**\$sp \$a0 = 2fact routine after updating \$v0 to 1 \* 1) \$a0 = 1bk f • return address to caller routine (bk f in fact routine) restored to \$ra from the stack previous value of \$a0 restored from the stack stack pointer updated to \$ra point to second call to fact \$a0 \$v0 5DV008 20091111 t:2C sl:51 Irwin CSE331 PSU

#### A Look at the Stack for \$a0 = 2. Part 5 Stack state after **←**\$sp old TOS execution of the second encounter with the second jr (return from fact routine after updating \$v0 to 2 \* 1 \* 1) return address to caller routine (main routine) restored to \$ra from the stack original value of \$a0 restored from the stack \$ra stack pointer updated to point to first call to fact \$a0 \$v0 5DV008 20091111 t:2C sl:52 Irwin CSE331 PSU

#### A Look at the Stack for \$a0 = 2. Part 5 Stack state after **←**\$sp old TOS execution of the second caller rt addr encounter with the second jr (return from \$a0 = 1 fact routine after updating \$v0 to 2 \* 1 \* 1) \$a0 = 0return address to caller routine (main routine) restored to \$ra from the stack original value of \$a0 caller\_rt addr \$ra restored from the stack stack pointer updated to point to first call to fact \$a0 5DV008 20091111 t:2C sl:53 Irwin CSE331 PSU

## Review: MIPS Instructions, so far

| Category                        | Instr                  | OpC    | Example              | Meaning                               |

|---------------------------------|------------------------|--------|----------------------|---------------------------------------|

| Arithmetic<br>(R & I<br>format) | add                    | 0 & 20 | add \$s1, \$s2, \$s3 | \$s1 = \$s2 + \$s3                    |

| ,                               | subtract               | 0 & 22 | sub \$s1, \$s2, \$s3 | \$s1 = \$s2 - \$s3                    |

|                                 | add immediate          | 8      | addi \$s1, \$s2, 4   | \$s1 = \$s2 + 4                       |

|                                 | shift left logical     | 0 & 00 | sll \$s1, \$s2, 4    | \$s1 = \$s2 << 4                      |

|                                 | shift right<br>logical | 0 & 02 | srl \$s1, \$s2, 4    | \$s1 = \$s2 >> 4 (fill with zeros)    |

|                                 | shift right arithmetic | 0 & 03 | sra \$s1, \$s2, 4    | \$s1 = \$s2 >> 4 (fill with sign bit) |

|                                 | and                    | 0 & 24 | and \$s1, \$s2, \$s3 | \$s1 = \$s2 & \$s3                    |

|                                 | or                     | 0 & 25 | or \$s1, \$s2, \$s3  | \$s1 = \$s2   \$s3                    |

|                                 | nor                    | 0 & 27 | nor \$s1, \$s2, \$s3 | \$s1 = not (\$s2   \$s3)              |

|                                 | and immediate          | С      | and \$s1, \$s2, ff00 | \$s1 = \$s2 & 0xff00                  |

|                                 | or immediate           | d      | or \$s1, \$s2, ff00  | \$s1 = \$s2   0xff00                  |

5DV008 20091111 t:2C sl:54 Irwin CSE331 PSU

# Review: MIPS Instructions, so far

| Category                  | Instr                            | OpC    | Example                 | Meaning                               |

|---------------------------|----------------------------------|--------|-------------------------|---------------------------------------|

| Data<br>transfer          | load word                        | 23     | lw \$s1, 100(\$s2)      | \$s1 = Memory(\$s2+100)               |

| (I format)                | store word                       | 2b     | sw \$s1, 100(\$s2)      | Memory(\$s2+100) = \$s1               |

| Cond.<br>branch<br>(I & R | br on equal                      | 4      | beq \$s1, \$s2, L       | if (\$s1==\$s2) go to L               |

| format)                   | br on not equal                  | 5      | bne \$s1, \$s2, L       | if (\$s1 !=\$s2) go to L              |

|                           | set on less<br>than<br>immediate | а      | slti \$s1, \$s2,<br>100 | if (\$s2<100) \$s1=1;<br>else \$s1=0  |

|                           | set on less<br>than              | 0 & 2a | slt \$s1, \$s2, \$s3    | if (\$s2<\$s3) \$s1=1;<br>else \$s1=0 |

| Uncond.                   | jump                             | 2      | j 2500                  | go to 10000                           |

| jump                      | jump register                    | 0 & 08 | jr \$t1                 | go to \$t1                            |

|                           | jump and link                    | 3      | jal 2500                | go to 10000; \$ra=PC+4                |

5DV008 20091111 t:2C sl:55

Irwin CSE331 PSU

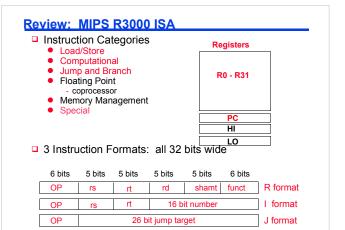

# Review: MIPS R3000 ISA

- □ Instruction Categories

Load/Store

Computational

Jump and Branch

Floating Point

coprocessor

Memory Management

Special

Registers

R0 - R31

PC HI

□ 3 Instruction Formats: all 32 bits wide

|                                 | 6 bits                     | 5 bits                      | 5 bits                        | 5 bits      | 5 bits                                 | 6 bits         |                                      |         |  |  |  |  |       |

|---------------------------------|----------------------------|-----------------------------|-------------------------------|-------------|----------------------------------------|----------------|--------------------------------------|---------|--|--|--|--|-------|

|                                 | OP                         | rs                          | rt                            | rd          | shamt                                  | funct          | R format                             |         |  |  |  |  |       |

|                                 | OP                         | rs                          | rt                            | 16 b        | oit number                             |                | I format                             |         |  |  |  |  |       |

|                                 | OP                         |                             | 26                            | bit jump ta | rget                                   |                | J format                             |         |  |  |  |  | <br>_ |

| DV008 20091111 t:2              | 2C sl:56                   |                             |                               |             |                                        |                | Irwin CSE                            | 331 PSU |  |  |  |  |       |

| Ator                            | nic E                      | <u>xcha</u>                 | nge S                         | upport      |                                        |                |                                      | _       |  |  |  |  |       |

| to a<br>cha                     | avoid c<br>ange d<br>Two m | data ra<br>epend<br>emory a | ices who<br>ling on haccesses | ere the i   | results on<br>ts happerent threa       | f the property |                                      |         |  |  |  |  |       |

| in a                            | a regis                    | ter for                     |                               |             |                                        |                | es a value<br>i.e., as one           |         |  |  |  |  |       |

|                                 | read ar                    | nd a me<br>rnative          | mory wri                      | te in a sin | ge would r<br>gle, uninto<br>specially | erruptabl      | oth a memory<br>e instruction.<br>ed |         |  |  |  |  |       |

|                                 | 11                         | \$t1,                       | 0(\$s1                        | )           | #                                      | load           | linked                               |         |  |  |  |  |       |

|                                 |                            |                             | 0(\$s1                        | )           | #                                      | store          |                                      |         |  |  |  |  |       |

| 11/23/06<br>5DV008 20091111 t:0 |                            | onal                        |                               |             |                                        | 57             | Irwin CSE                            | 431 PSU |  |  |  |  |       |

|                                 |                            |                             |                               |             |                                        |                |                                      |         |  |  |  |  |       |

#### Atomic Exchange with 11 and sc

□ If the contents of the memory location specified by the 11 are changed before the sc to the same address occurs, the sc fails (returns a zero)

```

try: add $t0, $zero, $s4  #$t0=$s4 (exchange value)

11 $t1, 0($s1)  #load memory value to $t1

sc $t0, 0($s1)  #try to store exchange

#value to memory, if fail

#$t0 will be 0

beq $t0, $zero, try  #try again on failure

add $s4, $zero, $t1  #load value in $s4

```

□ If the value in memory between the 11 and the sc instructions changes, then sc returns a 0 in \$t0 causing the code sequence to try again.

11/23/09

5DV008 20091111 t:02 sl:58

5DV008 20091111 t:2C sl:59

rwin CSE431 PSI