## 5DV118 Computer Organization and Architecture Umeå University Department of Computing Science

Stephen J. Hegner

# Topic 2: Instructions Part C: Control Flow

These slides are mostly taken verbatim, or with minor changes, from those prepared by

Mary Jane Irwin (www.cse.psu.edu/~mji)

of The Pennsylvania State University

[Adapted from Computer Organization and Design, 4th Edition,

Patterson & Hennessy, © 2008, MK]

## Key to the Slides

- The source of each slide is coded in the footer on the right side:

- Irwin CSE331 = slide by Mary Jane Irwin from the course CSE331 (Computer Organization and Design) at Pennsylvania State University.

- Irwin CSE431 = slide by Mary Jane Irwin from the course CSE431 (Computer Architecture) at Pennsylvania State University.

- Hegner UU = slide by Stephen J. Hegner at Umeå University.

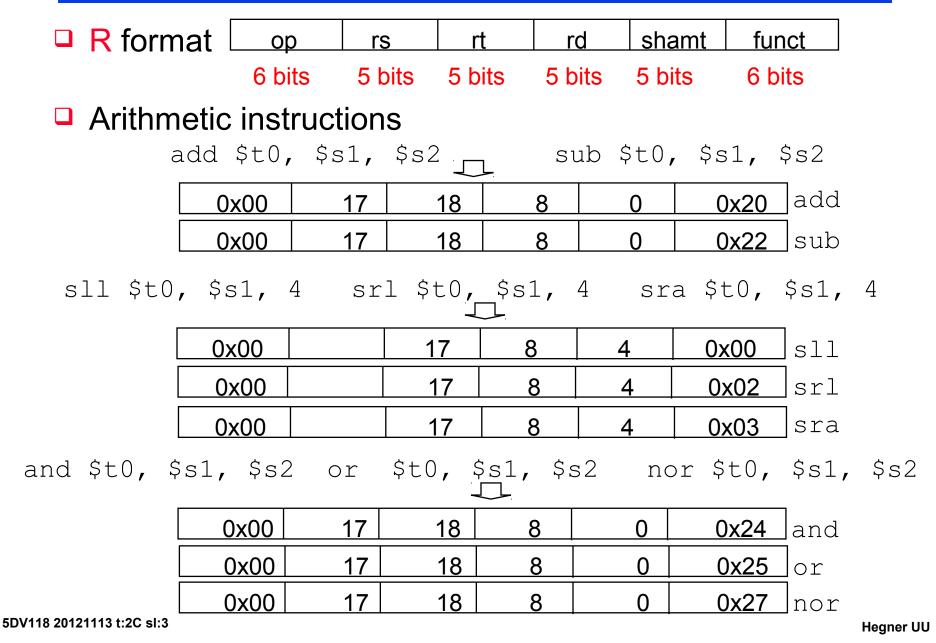

## **Review: R Format Instructions**

## **Review: I Format Instructions**

0x08

17

8

9

andi \$t0, \$s1, 0xff00

ori \$t0, \$s1, 0xff00

0x0c

17

8

0xff00

andi

0x0d

17

8

0xff00

ori

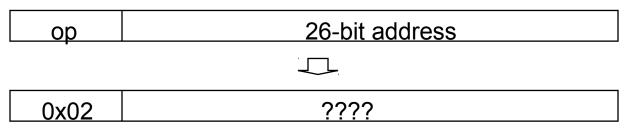

#### **MIPS Control Flow Instructions**

#### MIPS conditional branch instructions:

bne \$s0, \$s1, Lbl #go to Lbl if \$s0≠\$s1 beq \$s0, \$s1, Lbl #go to Lbl if \$s0=\$s1

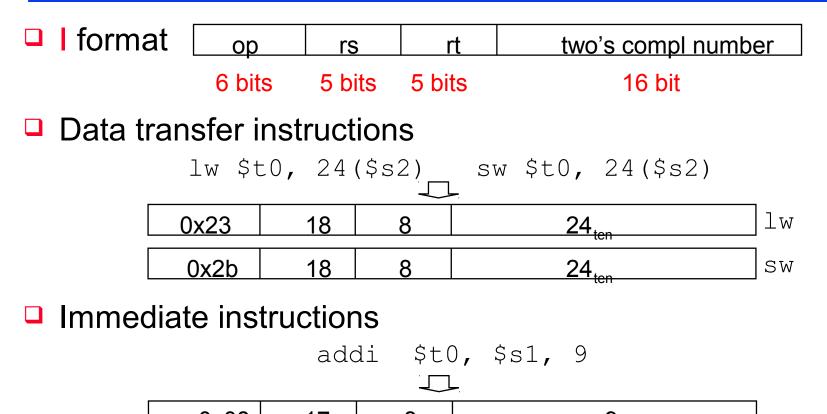

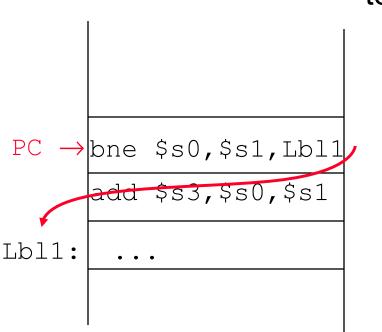

□ Instruction Format (I format):

How is the branch destination address specified?

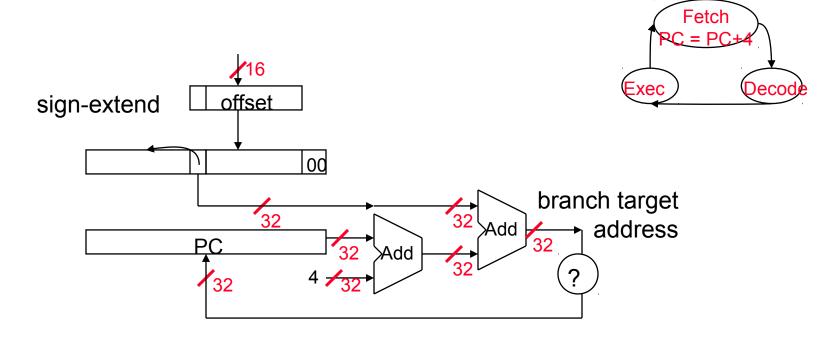

#### **Specifying Branch Destinations**

Could specify the memory address of the branch target

but that would require a 32-bit field

- Could use a "base" register and add to it the 16-bit offset

- which register?

- Instruction Address Register

(PC = program counter) its use is automatically implied by branch

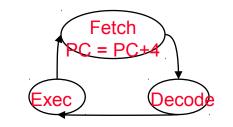

- PC gets updated (PC+4) during the Fetch cycle so that it holds the address of the next instruction

- limits the branch distance to

-2<sup>15</sup> to +2<sup>15</sup>-1 instr's from the (instruction after the) branch

- but most branches are local anyway

#### **Disassembling Branch Destinations**

#### □ The contents of the updated PC (PC+4) is

- added to the 16 bit branch offset;

- which is converted into a 32-bit value by concatenating two low-order zeros to make it a word address;

- and then sign-extending those 18 bits from the low order 16 bits of the branch instruction.

- The result is written into the PC if the branch condition is true as part of the Exec cycle - before the next Fetch cycle

#### **Offset Tradeoffs**

Why not just store the word offset in the low order 16 bits? Then the two low order zeros wouldn't have to be concatenated, it would be less confusing, …

- That would limit the branch distance to -2<sup>13</sup> to +2<sup>13</sup>-1 instructions from the (instruction after the) branch

- And concatenating the two zero bits costs us very little in additional hardware and has no impact on the clock cycle time

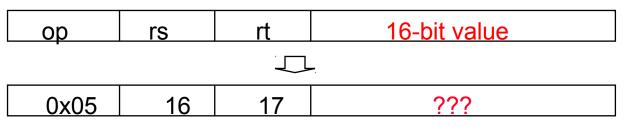

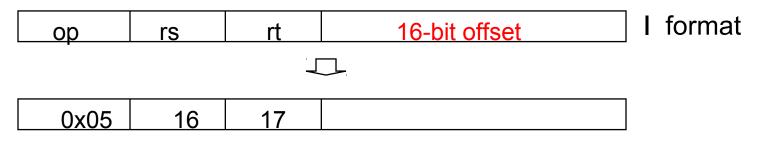

## **Assembling Branches Example**

#### Assembly code

bne \$s0, \$s1, Lbl1 add \$s3, \$s0, \$s1

Lbl1:

Machine Format of bne:

#### Remember

- After the bne instruction is fetched, the PC is updated so that it is addressing the add instruction

- The offset (plus 2 low-order zeros) is sign-extended and added to the (updated) PC

## **Assembling Branches Example**

#### Assembly code

bne \$s0, \$s1, Lb11 add \$s3, \$s0, \$s1

Lbl1:

Machine Format of bne:

## Remember

- After the bne instruction is fetched, the PC is updated so that it is addressing the add instruction

- The offset (plus 2 low-order zeros) is sign-extended and added to the (updated) PC

#### **In Support of Branch Instructions**

- We have beg, bne, but what about other kinds of branches (e.g., branch-if-less-than)? For this, we need yet another instruction, slt

- Set on less than instruction:

□ Instruction format (R format):

| 0x00 16 17 | 8 | 0x24 |

|------------|---|------|

|------------|---|------|

Alternate versions of slt

slti \$t0, \$s0, 25 # if \$s0 < 25 then \$t0=1 ...

sltu \$t0, \$s0, \$s1 # if \$s0 < \$s1 then \$t0=1 ...

sltiu \$t0, \$s0, 25 # if \$s0 < 25 then \$t0=1 ...

#### **More Branch Instructions**

Can use slt, beq, bne, and the fixed value of 0 in register \$zero to create other conditions

less than blt \$s1, \$s2, Label

- less than or equal to ble \$s1, \$s2, Label

greater than bgt \$s1, \$s2, Label

great than or equal to bge \$s1, \$s2, Label

- Such branches are included in the instruction set as pseudo instructions - recognized (and expanded) by the assembler

- Its why the assembler needs a reserved register (\$at)

#### **More Branch Instructions**

- Can use slt, beq, bne, and the fixed value of 0 in register \$zero to create other conditions

- less than blt \$s1, \$s2, Label

slt \$at, \$s1, \$s2 #\$at set to 1 if

bne \$at, \$zero, Label #\$s1 < \$s2

- less than or equal to ble \$s1, \$s2, Label

- greater than bgt \$s1, \$s2, Label

- great than or equal to bge \$s1, \$s2, Label

- Such branches are included in the instruction set as pseudo instructions - recognized (and expanded) by the assembler

- It is why the assembler needs a reserved register (\$at)

#### **Another Instruction for Changing Flow**

MIPS also has an unconditional branch instruction or jump instruction:

#qo to Lbl İ Lbl • Example: if (i!=j) h=i+j;else h=i-j; beq \$s0, \$s1, Else add \$s3, \$s0, \$s1 j Exit Else: sub \$s3, \$s0, \$s1 Exit: . . .

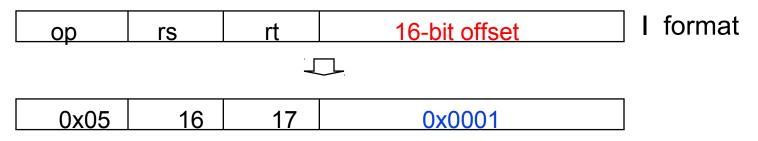

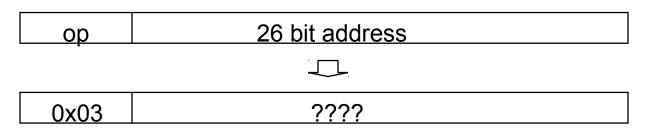

## **Assembling Jumps**

Instruction:

j Lbl #go to Lbl

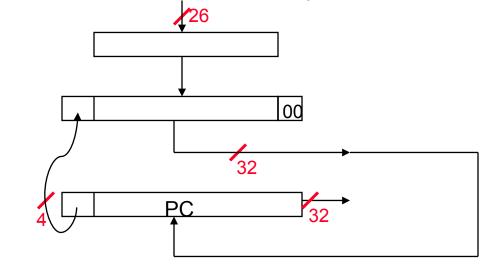

Machine Format (J format):

How is the jump destination address specified?

- As an absolute address formed by

- concatenating 00 as the 2 low-order bits to make it a word address

- concatenating the upper 4 bits of the current PC (now PC+4)

#### **Disassembling Jump Destinations**

- The low-order 26 bits of the jump instruction is converted into a 32-bit jump destination address by

- concatenating two low-order zeros to create an 28 bit (word) address and then concatenating the upper 4 bits of the current PC (now PC+4) to create a 32 bit (word) address

that is put into the PC prior to the next Fetch cycle

from the low order 26 bits of the jump instruction

#### **Branching Far Away**

What if the branch destination is further away than can be captured in 16 bits?

The assembler comes to the rescue – it inserts an unconditional jump to the branch target and inverts the condition

becomes

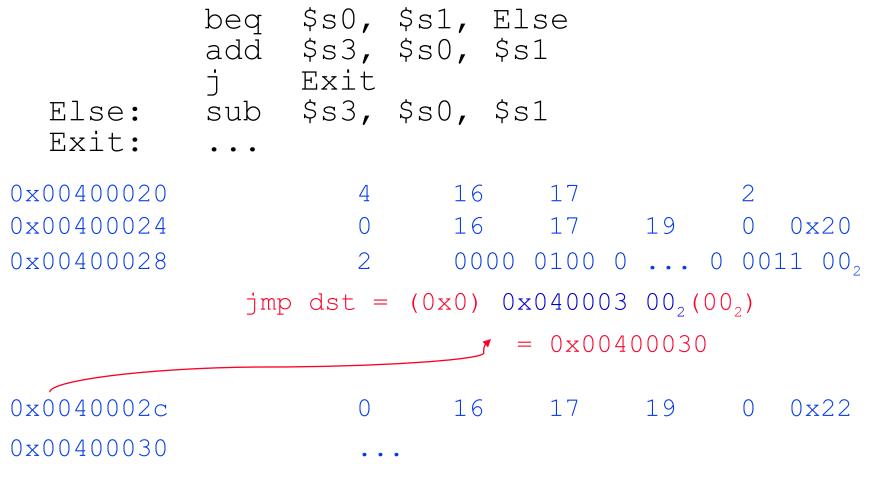

#### **Assembling Branches and Jumps**

Assemble the MIPS machine code for the following code sequence. Assume that the addr of the beq instr is 0x00400020<sub>hex</sub>

|       | beq   | \$s0, | \$s1, | Else |

|-------|-------|-------|-------|------|

|       | add   | \$s3, | \$s0, | \$s1 |

|       | j     | Exit  |       |      |

| Else: | sub   | \$s3, | \$s0, | \$s1 |

| Exit: | • • • |       |       |      |

#### **Assembling Branches and Jumps**

Assemble the MIPS machine code for the following code sequence. Assume that the addr of the beq instr is 0x00400020<sub>hex</sub>

#### **Compiling While Loops**

#### Compile the assembly code for the C while loop where i is in \$s0, j is in \$s1, and k is in \$s2

while (i!=k)

i=i+j;

Basic block – A sequence of instructions without branches (except at the end) and without branch targets (except at the beginning)

## **Compiling While Loops**

Compile the assembly code for the C while loop where i is in \$s0, j is in \$s1, and k is in \$s2

```

while (i!=k)

i=i+j;

```

| Loop: | beq | \$s0, | \$s2, | Exit |

|-------|-----|-------|-------|------|

|       | add | \$s0, | \$s0, | \$s1 |

|       | j   | Loop  |       |      |

| Exit: | • • | •     |       |      |

Basic block – A sequence of instructions without branches (except at the end) and without branch targets (except at the beginning)

### **Compiling Another While Loop**

Compile the assembly code for the C while loop where i is in \$s0, k is in \$s1, and the base address of the array save is in \$s2

Irwin CSE331 PSU

#### **Compiling Another While Loop**

Compile the assembly code for the C while loop where i is in \$s0, k is in \$s1, and the base address of the array save is in \$s2

| Loop: | sll  | \$t1, | \$s0,  | 2    |

|-------|------|-------|--------|------|

|       | add  | \$t1, | \$t1,  | \$s2 |

|       | lw   | \$t0, | 0(\$t] | 1)   |

|       | bne  | \$t0, | \$s1,  | Exit |

|       | addi | \$s0, | \$s0,  | 1    |

|       | j    | Loop  |        |      |

| Exit: | -    | •     |        |      |

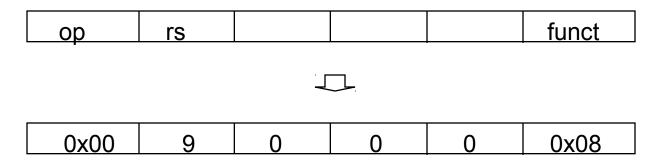

## Yet Another Instruction for Changing Flow

Most higher level languages have case or switch statements allowing the code to select one of many alternatives depending on a single value

Instruction:

```

jr $t1 #go to address in $t1

```

Machine format (R format):

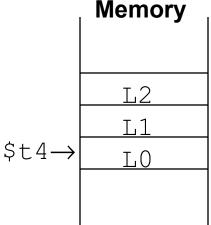

Compiling a Case (Switch) Statement

#### switch (k) { case 0: h=i+j; break; /\*k=0\*/ case 1: h=i+h; break; /\*k=1\*/ case 2: h=i-j; break; /\*k=2\*/ L2 Assume three sequential words in memory T.1 starting at the address in \$t4 have the

addresses of the labels L0, L1, and L2 and k is in \$s2

|     | add | \$t1 <b>,</b> | \$s2,  | \$s2 |  |

|-----|-----|---------------|--------|------|--|

|     | add | \$t1,         | \$t1,  | \$t1 |  |

|     | add | \$t1,         | \$t1,  | \$t4 |  |

|     | lw  | \$t0,         | 0(\$t] | 1)   |  |

|     | jr  | \$t0          |        |      |  |

| L0: | add | \$s3,         | \$s0,  | \$s1 |  |

|     | j   | Exit          |        |      |  |

| L1: | add | \$s3,         | \$s0,  | \$s3 |  |

|     | j   | Exit          |        |      |  |

| L2: | sub | \$s3,         | \$s0,  | \$s1 |  |

|     |     |               |        |      |  |

#\$t1 = 2\*k#\$t1 = 4 k#\$t1 = addr of JumpT[k] #\$t0 = JumpT[k] #jump based on \$t0 #k=0 so h=i+j#k=1 so h=i+h#k=2 so h=i-j

Exit: 5DV118 20121113 t:2C sl:25

#### **Programming Styles**

- Procedures (subroutines, functions) allow the programmer to structure programs making them

- easier to understand and debug and

- allowing code to be reused

- Procedures allow the programmer to concentrate on one portion of the code at a time

- parameters act as barriers between the procedure and the rest of the program and data, allowing the procedure to be passed values (arguments) and to return values (results)

#### Six Steps in Execution of a Procedure

- 1. Main routine (caller) places parameters in a place where the procedure (callee) can access them

- \$a0 \$a3: four argument registers

- 2. Caller transfers control to the callee

- 3. Callee acquires the storage resources needed

- 4. Callee performs the desired task

- 5. Callee places the result value in a place where the caller can access it

- \$v0 \$v1: two value registers for result values

- 6. Callee returns control to the caller

- \$ra: one return address register to return to the point of origin

## **Review: MIPS Register Naming Convention**

| Nick<br>Name       | Register<br>Number | Usage                      | Preserve<br>on call? |

|--------------------|--------------------|----------------------------|----------------------|

| \$zero             | 0                  | constant 0 (hardware)      | n.a.                 |

| \$at               | 1                  | reserved for assembler     | n.a.                 |

| \$v0 - \$v1        | 2-3                | returned values            | no                   |

| \$a0 <b>-</b> \$a3 | 4-7                | arguments                  | yes                  |

| \$t0 - \$t7        | 8-15               | temporaries                | no                   |

| \$s0 - \$s7        | 16-23              | saved values               | yes                  |

| \$t8 - \$t9        | 24-25              | temporaries                | no                   |

| \$k0 - \$k1        | 26-27              | reserved for OS            | n.a.                 |

| \$gp               | 28                 | global pointer             | yes                  |

| \$sp               | 29                 | stack pointer yes          |                      |

| \$fp               | 30                 | frame pointer yes          |                      |

| \$ra               | 31                 | return addr (hardware) yes |                      |

#### **Instruction for Calling a Procedure**

- MIPS procedure call instruction:

- jal ProcAddress #jump and link

- Saves PC+4 in register \$ra as the link to the following instruction to set up the procedure return

- Machine format (J format):

- Then can do procedure return with just

- jr \$ra #return

#### **Basic Procedure Flow**

For a procedure that computes the GCD of two values i (in \$t0) and j (in \$t1) gcd(i,j);

The caller puts the i and j (the parameters values) in \$a0 and \$a1 and issues a

jal gcd #jump to routine gcd

The callee computes the GCD, puts the result in \$v0, and returns control to the caller using

gcd:... #code to compute gcd jr \$ra #return

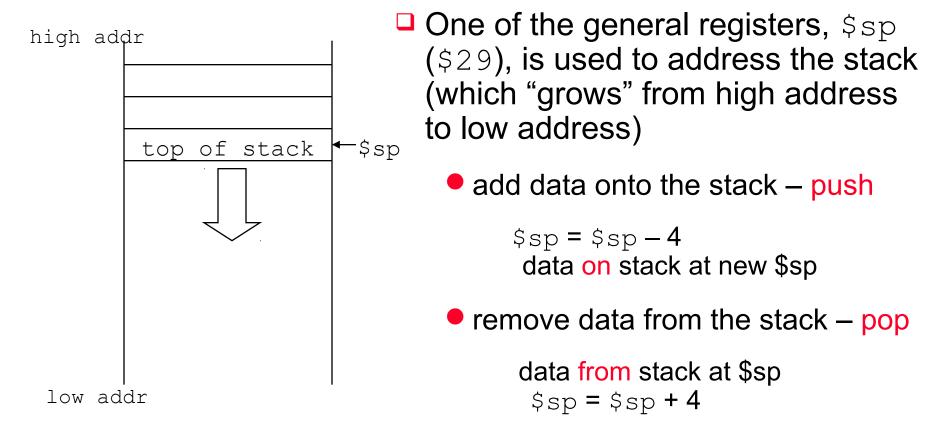

## **Spilling Registers**

What if the callee needs to use more registers than allocated to argument and return values?

callee uses a stack – a last-in-first-out queue

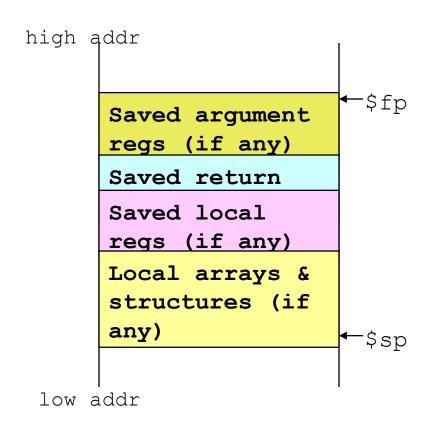

#### **Allocating Space on the Stack**

- The segment of the stack containing a procedure's saved registers and local variables is its procedure frame (aka activation record)

- The frame pointer (\$fp) points to the first word of the frame of a procedure – providing a stable "base" register for the procedure

- \$fp is initialized using \$sp

on a call and \$sp is restored

using \$fp on a return

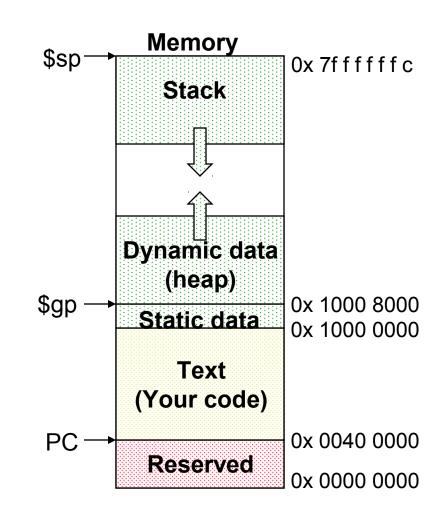

#### **Allocating Space on the Heap**

- There is a static data segment area for storing constants and other static variables (e.g., arrays)

- And a dynamic data segment (aka heap) area for structures that grow and shrink (e.g., linked lists)

- Allocate space on the heap with malloc() and free it with free() in C

#### **Compiling a C Leaf Procedure**

Leaf procedures are ones that do not call other procedures. Give the MIPS assembler code for int leaf\_ex (int g, int h, int i, int j) { int f; f = (g+h) - (i+j); return f; } where g, h, i, and j are in \$a0, \$a1, \$a2, \$a3

#### **Compiling a C Leaf Procedure**

Leaf procedures are ones that do not call other procedures. Give the MIPS assembler code for int leaf\_ex (int g, int h, int i, int j) { int f; f = (g+h) - (i+j); return f; } where g, h, i, and j are in \$a0, \$a1, \$a2, \$a3

| <pre>leaf_ex:</pre> | addi | \$sp,\$sp,-8   | #make stack room         |

|---------------------|------|----------------|--------------------------|

| _                   | SW   | \$t1,4(\$sp)   | #save \$t1 on stack      |

|                     | SW   | \$t0,0(\$sp)   | #save \$t0 on stack      |

|                     | add  | \$t0,\$a0,\$a1 |                          |

|                     | add  | \$t1,\$a2,\$a3 |                          |

|                     | sub  | \$v0,\$t0,\$t1 |                          |

|                     | lw   | \$t0,0(\$sp)   | <pre>#restore \$t0</pre> |

|                     | lw   | \$t1,4(\$sp)   | #restore \$t1            |

|                     | addi | \$sp,\$sp,8    | #adjust stack ptr        |

|                     | jr   | \$ra           |                          |

#### **Nested Procedures**

What happens to return addresses with nested procedures?

caller: jal rt\_1

next: . . .

rt\_1: bne \$a0, \$zero, to\_2

add \$v0, \$zero, \$zero

jr \$ra

to\_2: addi \$a0, \$a0, -1

jal rt\_2

jr \$ra

rt 2:

#### **Nested Procedures Outcome**

| caller:<br>next: | jal<br>•••       | rt_1<br>• |                                |

|------------------|------------------|-----------|--------------------------------|

| rt_1:            | bne<br>add<br>jr |           | \$zero, to_2<br>\$zero, \$zero |

| to_2:            | addi<br>jal      | •         | \$a0, -1                       |

| rt_2:            | • •              | •         |                                |

On the call to rt\_1, the return address (next in the caller routine) gets stored in \$ra. What happens to the value in \$ra (when i != 0) when rt\_1 makes a call to rt\_2?

#### **Saving the Return Address, Part 1**

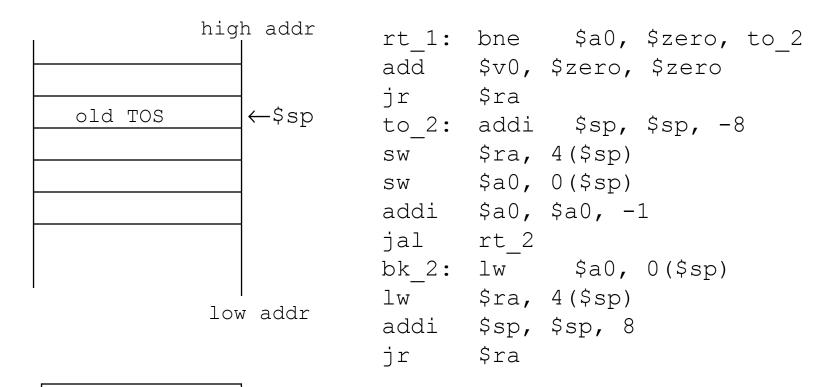

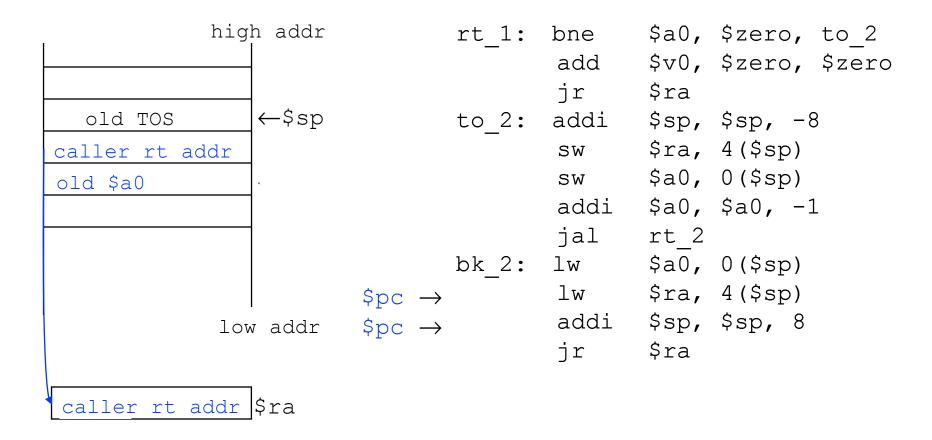

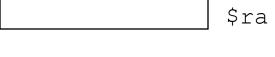

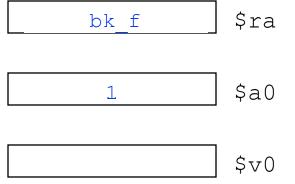

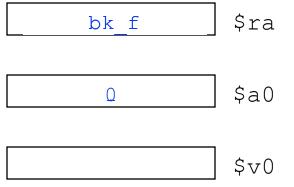

□ Nested procedures (i passed in \$a0, return value in \$v0)

Save the return address (and arguments) on the stack

#### Saving the Return Address. Part 1

□ Nested procedures (i passed in \$a0, return value in \$v0)

□ Save the return address (and arguments) on the stack

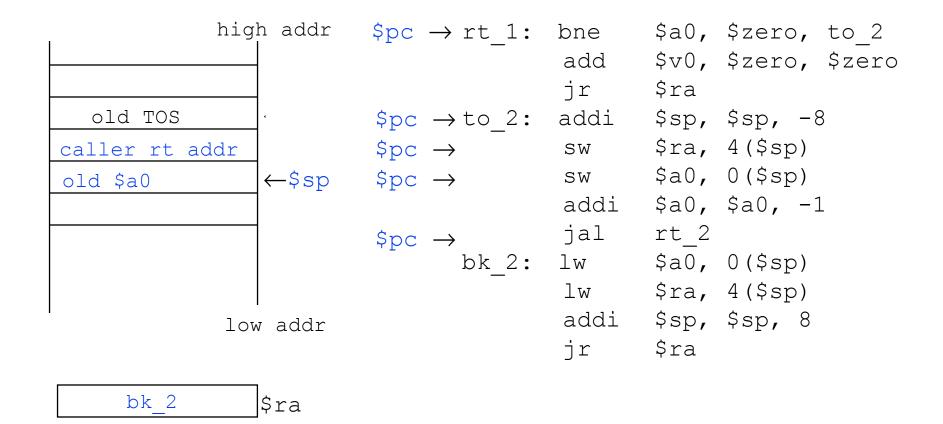

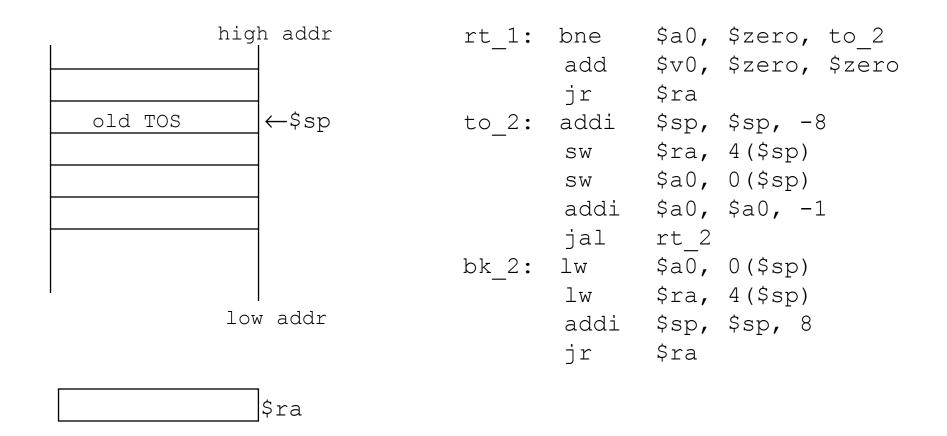

#### Saving the Return Address, Part 2

□ Nested procedures (i passed in \$a0, return value in \$v0)

Save the return address (and arguments) on the stack

#### Saving the Return Address, Part 2

□ Nested procedures (i passed in \$a0, return value in \$v0)

□ Save the return address (and arguments) on the stack

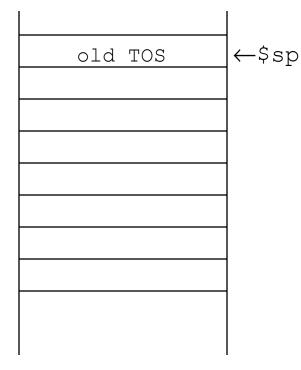

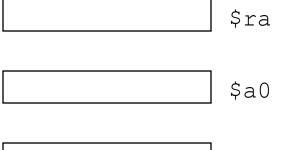

#### **Compiling a Recursive Procedure**

A procedure for calculating factorial

int fact (int n) {

if (n < 1) return 1;

else return (n \* fact (n-1)); }</pre>

□ A recursive procedure (one that calls itself!)

□ Assume n is passed in \$a0; result returned in \$v0

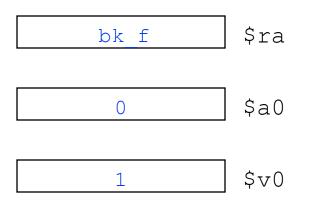

#### **Compiling a Recursive Procedure**

fact: addi \$sp, \$sp, -8 sw \$ra, 4(\$sp) sw \$a0, 0(\$sp) slti \$t0, \$a0, 1 beq \$t0, \$zero, L1 #if n >=1, go to L1 \$ra jr

#adjust stack pointer #save return address #save argument n #test for n < 1addi \$v0, \$zero, 1 #else return 1 in \$v0 addi \$sp, \$sp, 8 #adjust stack pointer #return to caller (1<sup>st</sup>)

L1: addi a0, a0, -1  $\#n \ge 1$ , so decrement n #call fact with (n-1)jal fact #this is where fact returns bk f: lw \$a0, 0(\$sp) #restore argument n lw \$ra, 4(\$sp) #restore return address addi \$sp, \$sp, 8 #adjust stack pointer mul \$v0, \$a0, \$v0 #\$v0 = n \* fact(n-1)jr \$ra #return to caller (2<sup>nd</sup>)

\$a0

\$v0

Stack state after execution of the first encounter with jal (second call to fact routine with \$a0 now holding 1)

- saved return address to caller routine (i.e., location in the main routine where *first* call to fact is made) on the stack

- saved original value of \$a0 on the stack

- Stack state after execution of the first encounter with jal (second call to fact routine with \$a0 now holding 1)

- saved return address to caller routine (i.e., location in the main routine where *first* call to fact is made) on the stack

- saved original value of \$a0 on the stack

\$v0

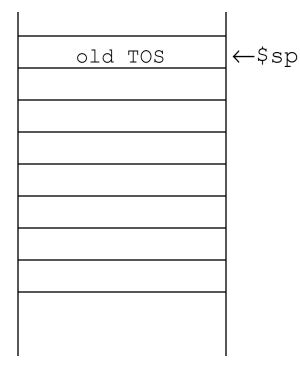

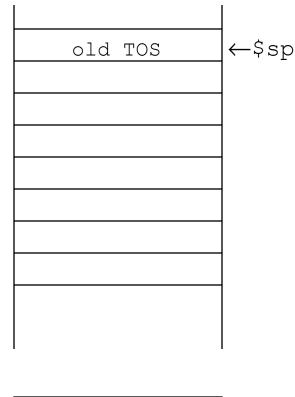

- Stack state after execution of the second encounter with jal (third call to fact routine with \$a0 now holding 0)

- save return address of instruction in caller routine (instruction after jal) on the stack

- save previous value of \$a0 on the stack

5DV118 20121113 t:2C sl:46

- Stack state after execution of the second encounter with jal (third call to fact routine with \$a0 now holding 0)

- saved return address of instruction in caller routine (instruction after jal) on the stack

- saved previous value of \$a0 on the stack

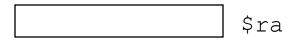

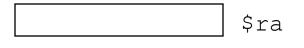

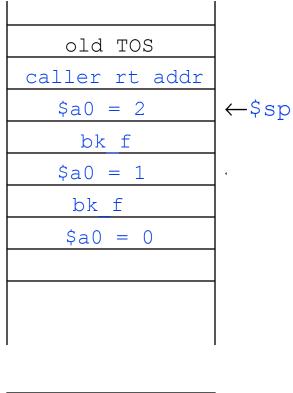

- Stack state after execution of the first encounter with the first jr (\$v0 initialized to 1)

- stack pointer updated to point to *third* call to fact

\$a0

- Stack state after execution of the first encounter with the first jr (\$v0 initialized to 1)

- stack pointer updated to point to *third* call to fact

\$a0

\$v0

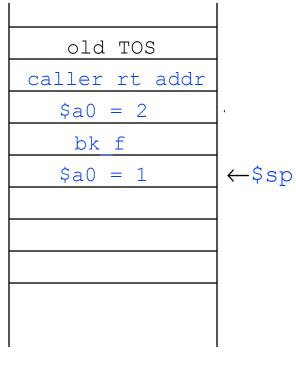

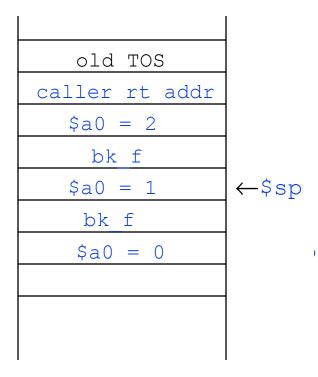

- Stack state after execution of the first encounter with the second jr (return from fact routine after updating \$v0 to 1 \* 1)

- return address to caller routine (bk\_f in fact routine) restored to \$ra from the stack

- previous value of \$a0 restored from the stack

- stack pointer updated to point to second call to fact

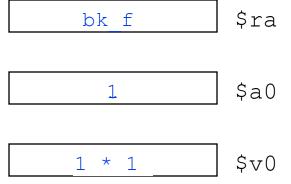

- Stack state after execution of the first encounter with the second jr (return from fact routine after updating \$v0 to 1 \* 1)

- return address to caller routine (bk\_f in fact routine) restored to \$ra from the stack

- previous value of \$a0 restored from the stack

- stack pointer updated to point to second call to fact

\$v0

Stack state after execution of the second encounter with the second jr (return from fact routine after updating \$v0 to 2 \* 1 \* 1)

- return address to caller routine (main routine) restored to \$ra from the stack

- original value of \$a0

restored from the stack

- stack pointer updated to point to *first* call to fact

- Stack state after execution of the second encounter with the second jr (return from fact routine after updating \$v0 to 2 \* 1 \* 1)

- return address to caller routine (main routine) restored to \$ra from the stack

- original value of \$a0

restored from the stack

- stack pointer updated to point to *first* call to fact

# **Review: MIPS Instructions, so far**

| Category                                        | Instr                     | ОрС    | Example              | Meaning                               |

|-------------------------------------------------|---------------------------|--------|----------------------|---------------------------------------|

| Arithmetic                                      | add                       | 0 & 20 | add \$s1, \$s2, \$s3 | \$s1 = \$s2 + \$s3                    |

| (R & I<br>format)                               |                           |        |                      |                                       |

| subtract<br>add immediate<br>shift left logical |                           | 0 & 22 | sub \$s1, \$s2, \$s3 | \$s1 = \$s2 - \$s3                    |

|                                                 |                           | 8      | addi \$s1, \$s2, 4   | \$s1 = \$s2 + 4                       |

|                                                 |                           | 0 & 00 | sll \$s1, \$s2, 4    | \$s1 = \$s2 << 4                      |

|                                                 | shift right<br>logical    | 0 & 02 | srl \$s1, \$s2, 4    | \$s1 = \$s2 >> 4 (fill with zeros)    |

|                                                 | shift right<br>arithmetic | 0 & 03 | sra \$s1, \$s2, 4    | \$s1 = \$s2 >> 4 (fill with sign bit) |

|                                                 | and                       | 0 & 24 | and \$s1, \$s2, \$s3 | \$s1 = \$s2 & \$s3                    |

|                                                 | or                        | 0 & 25 | or \$s1, \$s2, \$s3  | \$s1 = \$s2   \$s3                    |

|                                                 | nor                       | 0 & 27 | nor \$s1, \$s2, \$s3 | \$s1 = not (\$s2   \$s3)              |

|                                                 | and immediate             | С      | and \$s1, \$s2, ff00 | \$s1 = \$s2 & 0xff00                  |

|                                                 | or immediate              | d      | or \$s1, \$s2, ff00  | \$s1 = \$s2   0xff00                  |

# **Review: MIPS Instructions, so far**

| Category                             | Instr                            | ОрС    | Example                 | Meaning                               |

|--------------------------------------|----------------------------------|--------|-------------------------|---------------------------------------|

| Data<br>transfer<br>(I format)       | load word                        | 23     | lw \$s1, 100(\$s2)      | \$s1 = Memory(\$s2+100)               |

|                                      | store word                       | 2b     | sw \$s1, 100(\$s2)      | Memory(\$s2+100) = \$s1               |

| Cond.<br>branch<br>(I & R<br>format) | br on equal                      | 4      | beq \$s1, \$s2, L       | if (\$s1==\$s2) go to L               |

|                                      | br on not<br>equal               | 5      | bne \$s1, \$s2, L       | if (\$s1 !=\$s2) go to L              |

|                                      | set on less<br>than<br>immediate | а      | slti \$s1, \$s2,<br>100 | if (\$s2<100) \$s1=1;<br>else \$s1=0  |

|                                      | set on less<br>than              | 0 & 2a | slt \$s1, \$s2, \$s3    | if (\$s2<\$s3) \$s1=1;<br>else \$s1=0 |

| Uncond.<br>jump                      | jump                             | 2      | j 2500                  | go to 10000                           |

|                                      | jump register                    | 0 & 08 | jr \$t1                 | go to \$t1                            |

|                                      | jump and link                    | 3      | jal 2500                | go to 10000; \$ra=PC+4                |

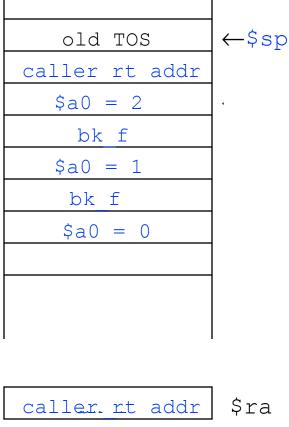

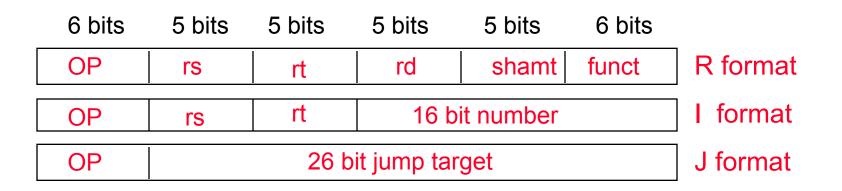

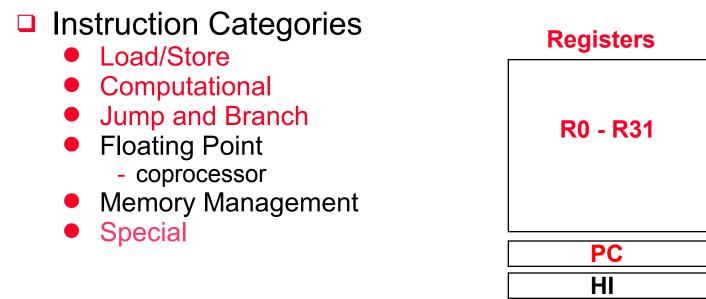

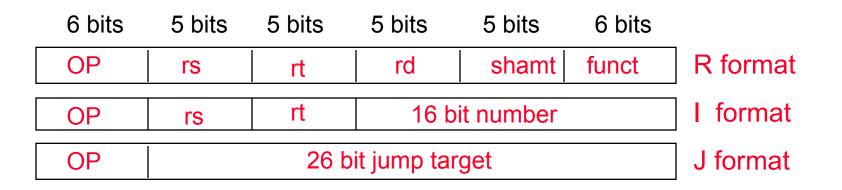

# **Review: MIPS R3000 ISA**

3 Instruction Formats: all 32 bits wide

#### **Atomic Exchange Support**

- Need hardware support for synchronization mechanisms to avoid data races where the results of the program can change depending on how events happen to occur

- Two memory accesses from different threads to the same location, and at least one is a write

- Atomic exchange (atomic swap) interchanges a value in a register for a value in memory atomically, i.e., as one operation (instruction)

- Implementing an atomic exchange would require both a memory read and a memory write in a single, uninterruptable instruction. An alternative is to have a pair of specially configured instructions

sc \$t0, 0(\$s1) #store conditional

#### Atomic Exchange with 11 and sc

If the contents of the memory location specified by the 11 are changed before the sc to the same address occurs, the sc fails (returns a zero)

```

□ Swap $s4 and memory($s1):

```

```

try: add $t0, $zero, $s4 #$t0=$s4 (exchange value)

ll $t1, 0($s1) #load memory value to $t1

sc $t0, 0($s1) #try to store exchange

#value to memory, if fail

#$t0 will be 0

beq $t0, $zero, try #try again on failure

add $s4, $zero, $t1 #load value in $s4

```

If the value in memory between the 11 and the sc instructions changes, then sc returns a 0 in \$t0 causing the code sequence to try again.

# **Review: MIPS R3000 ISA**

# 3 Instruction Formats: all 32 bits wide

# Addressing Modes Illustrated

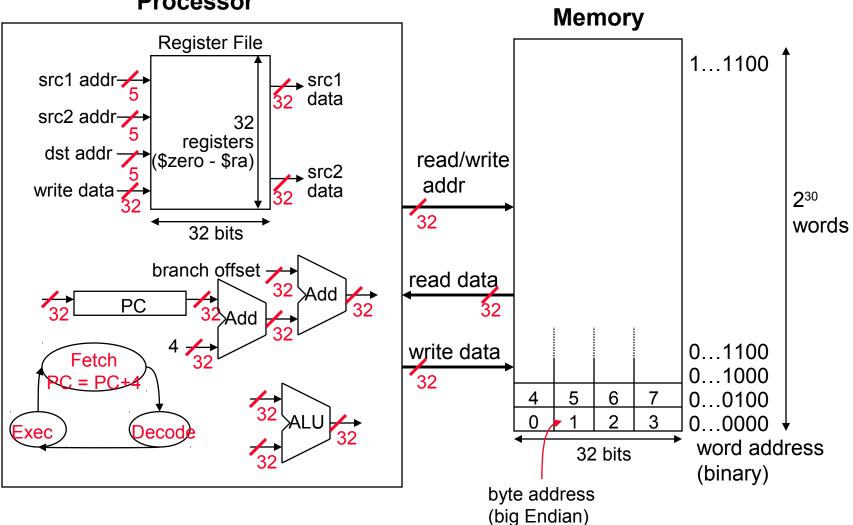

# **MIPS Organization So Far**

#### **Processor**